# MICROCART 2014-2015

Xilinx Tools (XPS, XSDK, and XISE) Setup and Walkthrough Author: Paul Gerver, Last updated: Feb 2015

# Table of Contents

| 1. | Intr  | oduction2                                                       |

|----|-------|-----------------------------------------------------------------|

| 2. | Setu  |                                                                 |

| 2. | 1.    | Coover 3050-11 and -122                                         |

| 2. | 2.    | ISU Remote Linux Servers (linux-X, research-x.ece.iastate.edu)2 |

| 2. | 3.    | User PC2                                                        |

| 3. | Xilir | x Platform Studio (XPS)                                         |

| 3. | 1.    | Creating a new XPS project                                      |

| 3. | 2.    | Opening an XPS Project                                          |

| 3. | 3.    | Synthesizing an XPS project7                                    |

| 3. | 4.    | Enabling Bluetooth (UARTO) / Editing MIO settings in XPS8       |

| 3. | 5.    | Enabling I2C for Sensor Board Use12                             |

| 4. | Xilir | x Software Development Kit (XSDK)14                             |

| 4. | 1.    | Exported System Hardware Platform14                             |

| 4. | 2.    | Creating a new Board Support Package (BSP)15                    |

| 4. | 3.    | Creating a new Application Project16                            |

| 4. | 4.    | Configuring JTAG                                                |

| 4. | 5.    | Launching an Application Project19                              |

| 5. | Run   | ning a MicroCART Task Example21                                 |

| 5. | 1.    | Zybo Board Terminal21                                           |

| 6. | Crea  | ating a Custom AXI IP Core (Custom Logic Block)25               |

| 6. | 1.    | Getting Started25                                               |

| 6. | 2.    | Xilinx Integrated Software Environment (XISE)29                 |

| 6. | 3.    | Simulating Logic with ModelSim or ISim                          |

| 6. | 4.    | Synthesizing Logic Core                                         |

| 6. | 5.    | Integrating new core into XPS                                   |

| 6. | 6.    | Accessing Core Registers in Software                            |

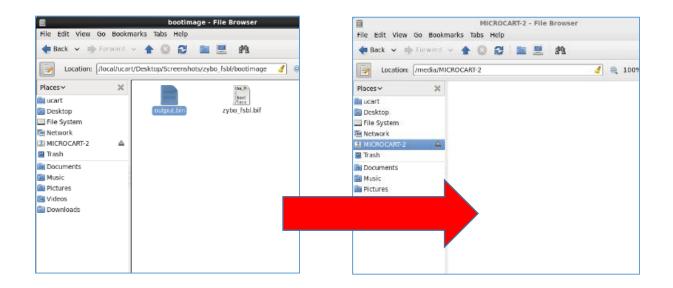

| 7. | Usir  | ng a MicroSD Card to program the Zybo Board38                   |

| 8. | FAC   |                                                                 |

## 1. Introduction

Welcome to the ultimate Xilinx Tools How-To guide! This guide should provide you with all the necessary knowledge and step-by-step instructions to get you making hardware configurations and programs with the different Xilinx tools.

There are three main tools that we will be learning: the Xilinx Platform Studio (XPS), Integrated Software Environment (ISE), and Software Development Kit (SDK). Students who have taken or are taking CprE 488: Embedded System Design may be familiar with these tools and should be a first stop for questions when working with the tools. Additionally, CprE 488 does has some helpful lab instructions, called MPs, and can also provide some helpful advice for working with these tools (http://class.ece.iastate.edu/cpre488/schedule.asp)

Because of MicroCART's use of the Diligent ZyBo board<sup>1</sup>, the following walkthrough will be centered on this development board, and different steps may be taken when working with a different board. The author will try his best to indicate when instances like these may arise.

## 2. Setup

Setting up access to the Xilinx tools is fairly straight forward given the machine the user is on. This guide will cover three types of machines: Coover 3050-11 and -12 computers (highly recommended), ISU's Remote Linux Servers, and a user's own PC

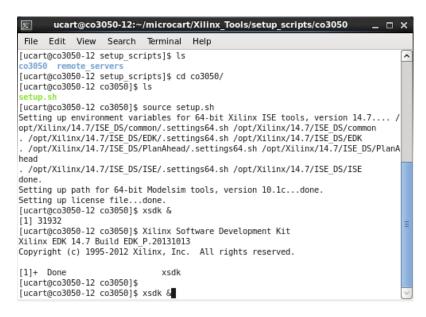

#### 2.1. Coover 3050-11 and -12

Two machines in the Distributed Sensing and Decision Making Lab (Coover 3050) come with the tools already installed. However, the following steps need to be taken in order to launch the program

- 1. In a terminal, enter source /opt/Xilinx/ISE/14.7/settings64.sh

- 2. OR source Xilinx\_Tools/setup\_scripts/co3050/setup.sh

#### 2.2. ISU Remote Linux Servers (linux-X, research-x.ece.iastate.edu)

- 3. source Xilinx\_Tools/setup\_scripts/remote\_servers/setup.sh

- 4. That's it! (Note: these servers are not good for programming the Zybo board when it comes time to launch a program on the board)

#### 2.3. User PC

Some users may opt to download the Xilinx tools on their own PCs for development, but this is not recommended.

5. Download the ISE Design Suite <u>here</u> (~6GB)

<sup>&</sup>lt;sup>1</sup> Please see the Diligent website for exact features and documents: <u>http://digilentinc.com/Products/Detail.cfm?Prod=ZYBO</u>

6. Ensure to install the ISE, XPS, and XSDK (The embedded package, I believe)

# 3. Xilinx Platform Studio (XPS)

XPS is the base program for creating a hardware description file (a .bit file) that will be loaded onto the Zybo board since it contains an ARM Cortex-A9 processor and a Zynq FPGA. Without a bit file, any program that is launched on the board may not be able to communicate with all the I/O and cool peripherals of the board. We'll first learn to start the XPS program, create a project targeted toward the Zybo (since this program can create bit files for more than just our board), and build our first bit file. Then, we will walkthrough setting up additional configurations that MicroCART uses

#### 3.1. Creating a new XPS project

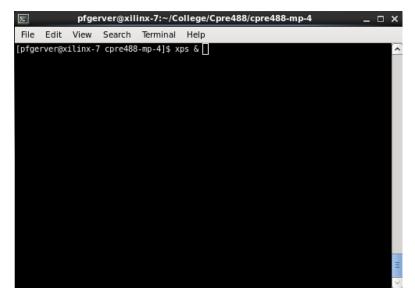

1. Once our environment and terminal have been setup, enter:  ${\rm xps}$  &

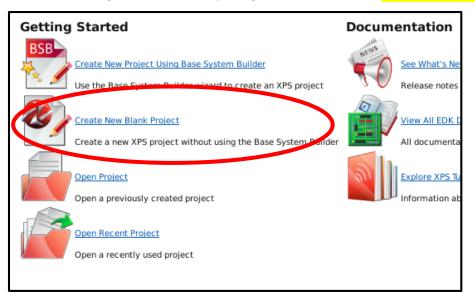

2. You should now be greeted with the opening window. Next click "Create New Blank Project"

- 3. The "Create New XPS Project" window should appear. Click Browse ... to select a location to save the project. (It is highly recommended to save the project in a "system" folder)

- 4. Select the Target Device fields to look exactly like they do below: Architecture = Zynq, Device Size = xc7z010, Package = clg400, Speed Grade = -1. Click OK when done.

|                                  |                                                             | <th></th>        |             |

|----------------------------------|-------------------------------------------------------------|------------------|-------------|

| arget device                     |                                                             |                  |             |

| <u>A</u> rchitecture             | Device Size                                                 | Pac <u>k</u> age | Speed Grade |

| zynq                             | \$ xc7z010                                                  | ¢ clg400         | \$ -1       |

|                                  | File (.mhs) from existing Pro                               |                  | Browse      |

| Import Design I Set Project Peri |                                                             | ath              |             |

| Import Design I Set Project Peri | pheral Repository Search Pa                                 | ath              |             |

| Import Design I Set Project Peri | pheral Repository Search Pa<br>ke File(instead of XPS gener | ath              | Browse      |

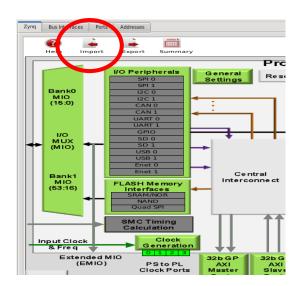

5. The Zynq System view should appear and look like the image below. Click Import to start importing the base definition for the Zybo.

6. Click the + button to add a new definition file and browse for the ZYBO\_zynq\_def.xml which can be found in "Xilinx\_Tools/XPS\_files/"

| Import Zynq Processing System Configurat                                | tions          |

|-------------------------------------------------------------------------|----------------|

| Select Configuration Template                                           |                |

| System Template (Configurations available in the installed area) :      |                |

| ZedBoard Development Board Template<br>ZC702 Development Board Template |                |

| ZC706 Development Board Template                                        |                |

|                                                                         |                |

|                                                                         |                |

| User Template (Configurations created by User) :                        |                |

|                                                                         |                |

|                                                                         | ÷              |

|                                                                         |                |

|                                                                         |                |

| Summary of selected Configuration:                                      |                |

| Janmary of Science configuration.                                       |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         |                |

|                                                                         | OK Cancel Help |

|                                                                         |                |

7. Once selected, click Open and click OK to start the import

| <b>?</b> 2          | Add Zynq Configuration Template File |         |   |   |            |               | × |

|---------------------|--------------------------------------|---------|---|---|------------|---------------|---|

| Look in:            | home/pfgerver/Desktop/XPS_walk       | \$<br>4 | ⇒ | 1 | <b>F</b> 2 |               |   |

| Computer            | system<br>ZYBO_zynq_def.xml          |         |   |   |            |               |   |

| File name: ZYB      | 0_zynq_def.xml                       | <br>    |   |   |            | <u>O</u> pen  | V |

| Files of type: *.xm | ı                                    | <br>    | [ | • | 8          | <u>C</u> ance | • |

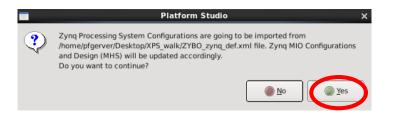

8. XPS will prompt you asking to update the MHS file, click Yes.

9. The default I/O controllers for the SD card, UART1 and other things will be selected and look like the following screen below.

## 3.2. Opening an XPS Project

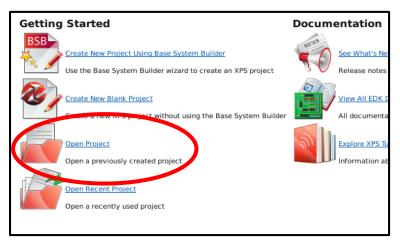

- 1. An XPS project can be opened in two ways:

- a. From the Getting Started window, click Open Project

- b. If a project is already open, click File -> Open Project

2. Navigate to the project .xmp file (i.e. task/zybo\_sensor\_board/system/system.xmp) and click Open

#### 3.3. Synthesizing an XPS project

**DECISION**: If users want to add additional features to use Bluetooth, I2C for the sensor board, or other configurations, please skip to the corresponding feature sections below before conducting the export process.

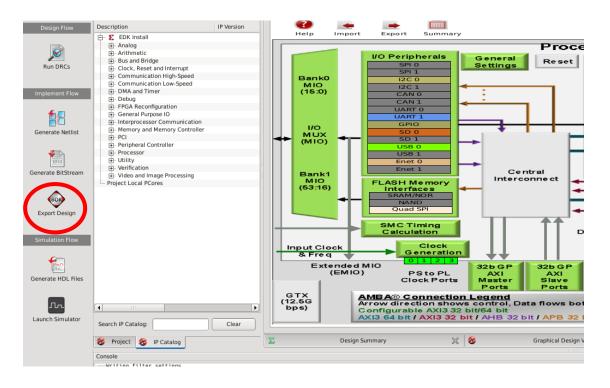

1. To create a bitfile, click Export Design (indicated by the red circle)

2. A Export to SDK / Launch SDK prompt will appear. Ensure XSDK is closed, if it was open, and click Export & Launch SDK (Skip to XSDK)

|           | Export to SDK / Launch SDK                                                        | х |

|-----------|-----------------------------------------------------------------------------------|---|

|           | nis dialog allows you to export hardware<br>atform information to be used in SDK. |   |

| ✓ Includ  | ie bitstream and BMM file                                                         |   |

|           | regenerate bitstream if necessary,<br>y take some time to finish.)                |   |

| Directory | location for hardware description files                                           |   |

| /home/pf  | fgerver/Desktop/XPS_walk/system/SDK/SDK_Export                                    |   |

|           | ielp Export & Launch SDK Cancel Export Only                                       |   |

**FORWARNING**: The exporting process can take several minutes to complete or over an hour depending on machine load and how much logic needs to programmed/routed.

#### 3.4. Enabling Bluetooth (UARTO) / Editing MIO settings in XPS

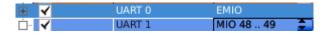

By default, UART1 is automatically configured for us when we imported the base Zybo definition file. UART1 is used on the board for receiving JTAG data and uses it as stdout and stdin for the board to communicate with the computer, when running a program. We will be enabling another UART, UART0, which will routed to a PMOD, so a program running on the board can send data via Bluetooth to the paired machine.

This walkthrough will setup UARTO communication routing for a BT2PMOD chip through the Zybo's PMOD-B port.

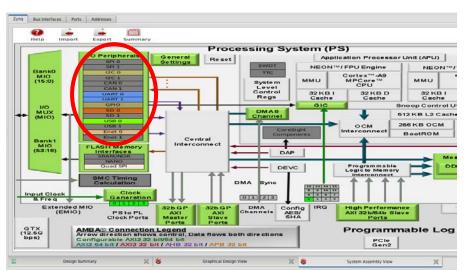

1. In XPS System View, click on the green I/O Peripherals box to bring up MIO Configuration box.

| In I -                | Devlahensi     | 10                                                                                                | 10               | Peripheral       | Signal           |

|-----------------------|----------------|---------------------------------------------------------------------------------------------------|------------------|------------------|------------------|

| hable                 | Peripheral     | 10                                                                                                | MIO 0            | IGPIO            | gpio[0]          |

| <                     | Quad SPI Flash | MIO 1 6                                                                                           | MIO 1            | Quad SPI Flash   | gspi0 ss b       |

| -                     | SRAM/NOR Flash | <select></select>                                                                                 | MIO 2            | Quad SPI Flash   | qspi0_io[0]      |

|                       | NAND Flash     | <select></select>                                                                                 | MIO 3            | Quad SPI Flash   | qspi0_io[1]      |

| ~                     | Enet 0         | <select>       MIO 16 27       <select>       MIO 28 39       <select></select></select></select> | MIO 4            | Quad SPI Flash   | qspi0_io[2]      |

| • 🖌                   | Enet 1         | <select></select>                                                                                 | MIO 5            | Quad SPI Flash   | gspi0_io[3]      |

| <b>√</b>              | USB 0          | MIO 28 39 🌻                                                                                       | MIO 6            | Quad SPI Flash   | qspi0_sclk       |

|                       | USB 1          | <select></select>                                                                                 | MIO 7            | GPIO             | gpio[7]          |

| <                     | SD 0           | MIO 40 45                                                                                         | MIO 8            | Quad SPI Flash   | gspi fbclk       |

|                       | SD 1           |                                                                                                   | MIO 9            | GPIO             | gpio[9]          |

|                       | UART 0         | <select></select>                                                                                 | MIO 10           | GPIO             | gpio[10]         |

| <ul> <li>✓</li> </ul> | UART 1         | MIO 48 49<br>EMIO<br><select></select>                                                            | MIO 10           | GPIO             | gpio[11]         |

| . 🖌                   | 12C 0          | EMIO                                                                                              | MIO 12           | GPIO             | gpio[12]         |

|                       | I2C 1          | <select></select>                                                                                 | MIO 12<br>MIO 13 | GPIO             | gpio[12]         |

|                       | SPI 0          | <select></select>                                                                                 | MIO 14           | GPIO             | gpio[14]         |

|                       | SPI 1          | <select></select>                                                                                 | MIO 15           | GPIO             | gpio[14]         |

|                       | CAN 0          | <select></select>                                                                                 | MIO 16           | Enet 0           | tx clk           |

|                       | CAN 1          | <select></select>                                                                                 | MIO 17           | Enet 0           | txd[0]           |

|                       | Trace          | <select></select>                                                                                 | MIO 17           | Enet 0           | txd[1]           |

|                       | Timer 0        | <select></select>                                                                                 | MIO 18           | Enet 0           | txd[2]           |

|                       | Timer 1        | <select></select>                                                                                 | MIO 19<br>MIO 20 | Enet 0           | txd[3]           |

|                       | Watchdog       |                                                                                                   | MIO 20<br>MIO 21 | Enet 0           | tx_ctl           |

|                       | PJTAG          | <select></select>                                                                                 | MIO 21<br>MIO 22 | Enet 0           | rx clk           |

| <                     | GPIO           |                                                                                                   | MIO 22<br>MIO 23 | Enet 0           | rx_cik<br>rxd[0] |

|                       |                |                                                                                                   | MIO 23           |                  | rxd[1]           |

|                       |                |                                                                                                   | MIO 24<br>MIO 25 | Enet 0<br>Enet 0 |                  |

|                       |                |                                                                                                   | MIO 25<br>MIO 26 |                  | rxd[2]           |

|                       |                |                                                                                                   | MIO 26<br>MIO 27 | Enet 0           | rxd[3]<br>rx ctl |

|                       |                |                                                                                                   | MIO 27<br>MIO 28 | Enet 0<br>USB 0  | data[4]          |

|                       |                |                                                                                                   |                  |                  |                  |

|                       |                |                                                                                                   | MIO 29           | USB 0            | dir              |

|                       |                |                                                                                                   | MIO 30           | USB 0            | stp              |

|                       |                |                                                                                                   | MIO 31           | USB 0            | nxt              |

|                       |                |                                                                                                   | MIO 32           | USB 0            | data[0]          |

|                       |                |                                                                                                   | MIO 33           | USB 0            | data[1]          |

|                       |                |                                                                                                   | MIO 34           | USB 0            | data[2]          |

|                       |                |                                                                                                   | MIO 35           | USB 0            | data[3]          |

|                       |                |                                                                                                   | MIO 36           | LISB 0           | clk              |

2. Enable the UARTO peripheral by clicking in the white box, and set the IO to EMIO. This makes the UART controller TX and RX pins go through the FPGA

3. When done, click Close

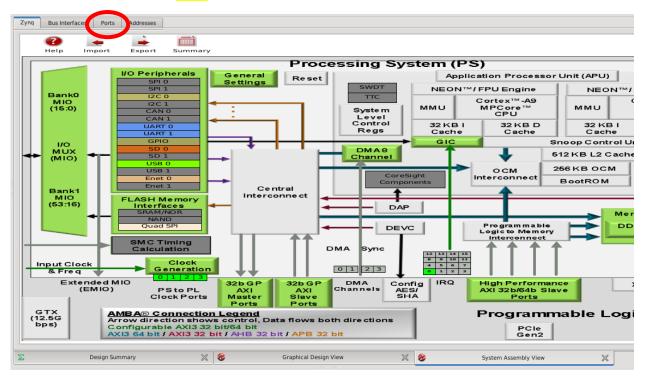

4. Next, click on the Ports tab to view system connections

5. Expand processing\_system7\_0 and the (IO\_IF) UART\_0 as seen below

| Zynq Bus Interfaces Ports       | Addresses                                         |     |     |

|---------------------------------|---------------------------------------------------|-----|-----|

| ame                             | Connected Port                                    | Di  | ire |

| FCLK CLK2                       |                                                   | 10  |     |

| FCLK CLK1                       |                                                   | 70  |     |

| - FCLK CLK0                     |                                                   | 10  |     |

| - FCLK CLKTRIG3 N               |                                                   | / I |     |

| - FCLK CLKTRIG2 N               |                                                   | I   |     |

| FCLK CLKTRIG1 N                 |                                                   | 7 I |     |

| FCLK CLKTRIGO N                 |                                                   | / I |     |

| FCLK RESET3 N                   |                                                   | 70  |     |

| FCLK RESET2 N                   |                                                   | / 0 |     |

| FCLK RESETI N                   |                                                   | 10  |     |

| FCLK RESETO N                   |                                                   | / 0 |     |

| IRQ_F2P                         | L to H: No Connection                             | Ī   |     |

| Core0 nFIQ                      |                                                   | I   |     |

| - Core0 nIRQ                    |                                                   | I   |     |

| Core1_nFIQ                      |                                                   | I   |     |

| - Core1 nIRQ                    |                                                   | I   |     |

| IRQ_P2F_QSPI                    |                                                   | / 0 |     |

| IRQ_P2F_GPIO                    |                                                   | 10  |     |

| IRQ_P2F_USB0                    |                                                   | / 0 |     |

| IRQ_P2F_ENET0                   |                                                   | 70  |     |

|                                 |                                                   | 0   |     |

| ···· IRQ_P2F_SDI00              |                                                   | 10  |     |

| IRQ_P2F_I2C0                    |                                                   | / 0 |     |

| ···· IRQ_P2F_UART0              |                                                   | 10  |     |

| IRQ_P2F_UART1                   |                                                   |     |     |

| (IO_IF) MEMORY_0                | Connected to External Ports                       | ۲.  |     |

| (IO_IF) PS_REQUIRED_EXTERNAL_IO | Connected to External Ports                       |     |     |

|                                 | Connected to External Ports                       | ٦   |     |

| ···· UART0_TX                   | External Ports::processing_system7_0_UART0_TX_pin | / 0 |     |

| UARTO_RX                        |                                                   | I   |     |

|                                 | Not connected to External Ports                   | ٢   |     |

| ± ·· (IO_IF) USBIND_0           | Not connected to External Ports                   | ٦   |     |

| clock_generator_0               |                                                   |     |     |

| - reset 0                       |                                                   |     |     |

- Ð **1** Port Filters >> By Interface Direction Class F ▲ Range Filters • • • • • • • • • • • • • V BUS 10 NONE / 0 ✓ 10 NONE 10 By Connection NONE / 1 Defaults Check This CLK 71 onnected NONE Unconnected / 1 NONE By Class Clocks Only / 0 CLK Clocks CLK Resets Only CLK Resets CLK Interrupts Only Interrupts Others By Direction Inputs RST Outputs / 0 RST ✓ InOuts / 0 RST 70 RST INTERRUPT Ι INTERRUPT INCOME DALLER

- i. NOTE: if the sections are not there, you need to enable viewing all connections. This can be done by clicking on the << button and **checking** the Defaults connection box

- 6. Right-click on the UARTO\_TX and UARTO\_RX connections and click Make External. This tells the system that we want to connect those ports to an external source (our PMOD)

- 7. Once the ports are external, move to the top of the ports list and expand External Ports

| lame                                | Connected Port                                            | Direction | Ra           |  |

|-------------------------------------|-----------------------------------------------------------|-----------|--------------|--|

| External Ports                      |                                                           |           |              |  |

| CLK_N                               | clock_generator_0::CLKIN                                  | / I       | ۲            |  |

| ···· CLK_P                          | clock_generator_0::CLKIN                                  | 7 I       |              |  |

| processing_system7_0_DDR_Addr       | processing_system7_0::[MEMORY_0]::DDR_Addr                | / 10      | (1)          |  |

| … processing_system7_0_DDR_BankAddr | processing_system7_0::[MEMORY_0]::DDR_BankAddr            | 7 10      | 12           |  |

| processing_system7_0_DDR_CAS_n      | processing_system7_0::[MEMORY_0]::DDR_CAS_n               | / 10      | ۲            |  |

| — processing_system7_0_DDR_CKE      | processing_system7_0::[MEMORY_0]::DDR_CKE                 | 7 10      |              |  |

| processing_system7_0_DDR_CS_n       | processing_system7_0::[MEMORY_0]::DDR_CS_n                | / 10      |              |  |

| processing_system7_0_DDR_Clk        | processing_system7_0::[MEMORY_0]::DDR_Clk                 | 7 10      |              |  |

| processing_system7_0_DDR_Clk_n      | processing_system7_0::[MEMORY_0]::DDR_Clk_n               | / 10      |              |  |

| processing_system7_0_DDR_DM         | processing_system7_0::[MEMORY_0]::DDR_DM                  | 7 10      | - Ē <i>l</i> |  |

| processing_system7_0_DDR_DQ         | processing_system7_0::[MEMORY_0]::DDR_DQ                  | / 10      | 1            |  |

| processing_system7_0_DDR_DQS        | processing_system7_0::[MEMORY_0]::DDR_DQS                 | 7 10      |              |  |

| processing system7 0 DDR DQS n      | processing_system7_0::[MEMORY_0]::DDR_DQS_n               | / 10      | I            |  |

| processing_system7_0_DDR_DRSTB      | processing_system7_0::[MEMORY_0]::DDR_DRSTB               | 7 10      |              |  |

| — processing_system7_0_DDR_ODT      | processing_system7_0::[MEMORY_0]::DDR_ODT                 | / 10      | ۲            |  |

| processing_system7_0_DDR_RAS_n      | processing_system7_0::[MEMORY_0]::DDR_RAS_n               | 7 10      |              |  |

| processing_system7_0_DDR_VRN        | processing_system7_0::[MEMORY_0]::DDR_VRN                 | / 10      | <b>(</b>     |  |

| processing_system7_0_DDR_VRP        | processing_system7_0::[MEMORY_0]::DDR_VRP                 | 7 10      |              |  |

| processing_system7_0_DDR_WEB_pin    | processing_system7_0::[MEMORY_0]::DDR_WEB                 | / 0       | ۲            |  |

| processing_system7_0_MIO            | processing_system7_0::[PS_REQUIRED_EXTERNAL_IO]::MIO      | 7 10      | - Ē          |  |

| processing_system7_0_PS_CLK_pin     | processing_system7_0::[PS_REQUIRED_EXTERNAL_IO]::PS_CLK   | / I       | Test         |  |

| processing_system7_0_PS_PORB_pin    | processing_system7_0::[PS_REQUIRED_EXTERNAL_IO]::PS_PORB  | 71        |              |  |

| processing_system7_0_PS_SRSTB_pin   | processing_system7_0::[PS_REQUIRED_EXTERNAL_IO]::PS_SRSTB | / I       |              |  |

| processing_system7_0_UART0_RX_pin   | processing_system7_0::[UART_0]::UART0_RX                  | 7 I       | ٦            |  |

| processing_system7_0_UART0_TX_pin   | processing_system7_0::[UART_0]::UART0_TX                  | / 0       | •            |  |

- 8. Take note of the **Name** for these (processing\_system7\_0\_UART0\_RX\_pin). We will be using this to assign the proper pin location

- 9. On the left side of XPS, there should be a <u>Project Platform</u> window with two tabs at the bottom: Project and IP Catalog. Click on Project

- 10. Double click on UCF File: data/system.ucf under the Project Files list (highlighted in blue)

| Project                                                                                      | +00              |

|----------------------------------------------------------------------------------------------|------------------|

| Platform                                                                                     |                  |

| Project Files                                                                                |                  |

| <ul> <li>MHS File: system.mhs</li> </ul>                                                     |                  |

| <ul> <li>UCF File: data/system.ucf</li> </ul>                                                | all and a set of |

| ···· IMPACT Command File: etc/dov                                                            |                  |

| <ul> <li>Implementation Options File: e</li> <li>Bitgen Options File: etc/bitgen.</li> </ul> |                  |

| Elf Files                                                                                    | ul               |

| - Project Options                                                                            |                  |

| Device: xc7z010clg400-1                                                                      |                  |

| Netlist: TopLevel                                                                            |                  |

| Implementation: XPS (Xflow)                                                                  |                  |

| HDL: VHDL                                                                                    |                  |

| Sim Model: BEHAVIORAL                                                                        |                  |

| Design Summary                                                                               |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

|                                                                                              |                  |

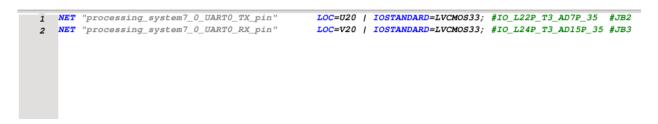

The system.ucf file will open (probably blank) where you can put in pin assignments for external ports. For this specific case, we will assign the TX and RX pins to PMOD-B pins 2 and 3. It should look something like this below.

**NOTE:** the pins are assigned by Name and Location (please see the Zybo board spec sheet PMOD descriptions and the Master UCF file for all pin locations)

- 12. Finally, click Export Design

- 13. A Export to SDK / Launch SDK prompt will appear. Ensure XSDK is closed, if it was open, and click Export & Launch SDK (Move to Section 4: XSDK )

**FORWARNING**: The exporting process can take several minutes to complete or over an hour depending on machine load and how much logic needs to programmed.

| Export to SDK / Launch SDK                                                            | × |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

| This dialog allows you to export hardware platform information to be used in SDK.     |   |  |  |  |  |  |  |

| ✓ Include bitstream and BMM file                                                      |   |  |  |  |  |  |  |

| (XPS will regenerate bitstream if necessary,<br>and it may take some time to finish.) |   |  |  |  |  |  |  |

| Directory location for hardware description files                                     |   |  |  |  |  |  |  |

| /home/pfgerver/Desktop/XPS_walk/system/SDK/SDK_Export                                 |   |  |  |  |  |  |  |

| Help Export & Launch SDK                                                              | ] |  |  |  |  |  |  |

## 3.5. Enabling I2C for Sensor Board Use

The Zybo board has two I2C controllers that can be used to communicate with peripherals. For example, MicroCART uses one I2C controller to talk with the SparkFun 9-degrees of freedom sensor board (MPU9150). A LOT of time has been spent getting the proper configurations for this to work, so PLEASE follow the instructions carefully.

1. In XPS System View, click on the green I/O Peripherals box to bring up MIO Configuration box.

- 2. VERY IMPORTANT Check the Show I/O Standard Options

- 3. Chance I2CO's IO to MIO 10..11, set LVCMOS 3.3V for both Bank 0 and 1, **ENABLE** Pullup on MIO 10 and 11

| nq PS Confi |                |                   | MIO Configura | tandard Options | Bank 0 IO Voltage: | LVCMOS 3.3V | Bank 1 IO Voltage: | LVCMOS 3.3V |

|-------------|----------------|-------------------|---------------|-----------------|--------------------|-------------|--------------------|-------------|

| able        | Peripheral     | 10                | 10            | Peripheral      | Signet             | IO Type     | Speed              | Pullup      |

| · 🖌         | Quad SPI Flash | MIO 1 6           | MIO 0         | GPIO            | gpio[0]            | LVCMOS 3.3V | 🗘 Islow 🗘          | disabled    |

| -           | SRAM/NOR Flash | <select></select> | MIO 1         | Quad SPI Flash  | qspi0_ss_b         | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

| -           | NAND Flash     | <select></select> | MIO 2         | Quad SPI Flash  | qspi0_io[0]        | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

| - 🖌         | Enet 0         | MIO 16 27 📮       | MIO 3         | Quad SPI Flash  | qspi0_io[1]        | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | Enet 1         | <select></select> | MIO 4         | Quad SPI Flash  | qspi0_io[2]        | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

| ×           | USB 0          | MIO 28 39 🗘       | MIO 5         | Quad SPI Flash  | qspi0_io[3]        | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | USB 1          | <select></select> | MIO 6         | Quad SPI Flash  | qspi0_sclk         | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

| · 🖌         | SD 0           | MIO 40 45 🗘       | MIO 7         | GPIO            | gpio[7]            | LVCMOS 3.3V | 韋 slow 📮           | disabled    |

|             | SD 1           | <select></select> | MIO 8         | Quad SPI Flash  | qspi_fbclk         | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | UART 0         | <select></select> | MIO 9         | 0.10            | [gpio[9]           | LVCMOS 3.3V | SIOW               | disabled    |

| ×           |                | 10 40             | MIC 10        | 12C 0           | scl                | LVCMOS 3.3V | 🗘 slow 🗘           | enabled     |

| <b>V</b>    | 12C 0          | MIO 10 11 🗘       | MIO 11        | 12C 0           | sda                | LVCMOS 3.3V | 🔷 slow 🗘           | enabled     |

|             | 12C 1          | <select></select> | 1.0.12        | GPIO            | gpio[12]           | LVCMOS 3.3V | 🗘 slow 🗘           | disabled    |

|             | SPLO           | <select></select> | MIO 13        | GHO             |                    | WOMOG 2 PM  |                    | disabled    |

|             | SPI 1          | <select></select> | MIO 14        | GPIO            | gpio[14]           | LVCMOS 3.3V | slow 🗘             | disabled    |

|             | CAN 0          | <select></select> | MIO 15        | GPIO            | gpio[15]           | LVCMOS 3.3V | 🗘 slow 🗘           | disabled    |

|             | CAN 1          | <select></select> | MIO 16        | Enet 0          | tx_clk             | LVCMOS 3.3V | 🛊 fast 🛊           | disabled    |

|             | Trace          | <select></select> | MIO 17        | Enet 0          | txd[0]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | Timer 0        | <select></select> | MIO 18        | Enet 0          | txd[1]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | Timer 1        | <select></select> | MIO 19        | Enet 0          | txd[2]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | Watchdog       | <select></select> | MIO 20        | Enet 0          | txd[3]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             | PJTAG          | <select></select> | MIO 21        | Enet 0          | tx_ctl             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

| <b>~</b>    | GPIO           |                   | MIO 22        | Enet 0          | rx_clk             | LVCMOS 3.3V | 🛊 fast 🗘           | disabled    |

|             |                |                   | MIO 23        | Enet 0          | rxd[0]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 24        | Enet 0          | rxd[1]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 25        | Enet 0          | rxd[2]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 26        | Enet 0          | rxd[3]             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 27        | Enet 0          | rx_ctl             | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 28        | USB 0           | data[4]            | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 29        | USB 0           | dir                | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 30        | USB 0           | stp                | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 31        | USB 0           | nxt                | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 32        | USB 0           | data[0]            | LVCMOS 3.3V | 🗘 fast 🗘           | disabled    |

|             |                |                   | MIO 33        | USB 0           | data[1]            |             |                    | disabled    |

|             |                |                   | MIO 34        | USB 0           | data[2]            |             |                    | disabled    |

|             |                |                   | 4             |                 |                    |             |                    | •           |

**NOTE:** MIO10 and 11 automatically route to PMOD-F pins 2 (SCL) and 3 (SDA). If you'd like to assign them to alternative PMODS, Change the connection to EMIO and preform pin assignment process starting at Step 4 for UARTO configuration.

4. Start the Export Design process (Synthesizing an XPS Project)

## 4. Xilinx Software Development Kit (XSDK)

The XSDK is the main program used to create software applications for the Zybo board as well as flash the FPGA bitstream file onto the board. There are three main things required for a project:

- 1. A system hardware platform (automatically exporting design from XPS)

- 2. A Board Support Package (Contains software functions for interacting with the Processing System controllers i.e. UART and I2C or logic cores on the FPGA)

- 3. An Application Project (A simple hello world, an NES emulator, or something else)

As mentioned above the system\_hw\_platform is imported for us by XPS when we export our bitstream file to the XSDK. We'll walkthrough the other two items as well as programming the FPGA from within the XSDK.

#### 4.1. Exported System Hardware Platform

- 1. Whenever Export & Open XSDK or Export Only are clicked, the bitstream file will be generated and automatically open up XSDK and/or update XSDK if it is open.

- 2. When opening XSDK, you will be prompted for a workspace. A good naming scheme is to put the workspace into a folder called "sw". Either give a location of a new workspace or select a task's sw directory to open up it up.

**DO NOT:** check "Use this as the default and do not ask again"

3. Click OK when a proper directory has been given.

| Workspace Launcher                                                                                                    | ×         |

|-----------------------------------------------------------------------------------------------------------------------|-----------|

| Select a workspace                                                                                                    |           |

| Xilinx SDK stores your projects in a folder called a workspace.<br>Choose a workspace folder to use for this session. |           |

| Workspace: //home/pfgerver/Desktop/XPS_walk/sw                                                                        | Browse    |

| Use this as the default and do not ask again NO!!!                                                                    |           |

|                                                                                                                       | Cancel OK |

4. View the Eclipse-based XSDK. As you can see, the system\_hw\_platform is already in there for us.

| 10                                 | C/C++ - system_hw_platform/system.xml - Xilinx                                                 |

|------------------------------------|------------------------------------------------------------------------------------------------|

| File Edit Source Refactor Navigate | Search Run Project Xilinx Tools Window Help                                                    |

| ) <b></b>                          | ੶ ] @ ~ @ ~ ፪ ~ @ ~ ] ☆ ~ Q ~ Q ~ ] ≈ ] □ ] # ⊠ ] & ] ⊘ / ~ ] □                                |

| Project Explorer 🕱 🗖               | system.xml 🛛                                                                                   |

| E 😫 🔻 '                            | system_hw_platform Hardware Platform Specification                                             |

|                                    | Design Information                                                                             |

| s7_init.c                          | Target FPGA Device: xc7z010                                                                    |

| ⊫ ps7_init.h                       | Created With: EDK 14.7                                                                         |

| ps7_init.html                      | Created On: Mon Dec 1 17:58:55 2014                                                            |

| ps7_init.tcl                       | XPS Design Report: file:///home/pfgerver/Desktop/XPS_walk/system/SDK/SDK_Export/hw/system.html |

| i system.bit                       |                                                                                                |

| system.xml                         | Address Map for processor ps7_cortexa9_0                                                       |

|                                    | ps7 uart 0 0xe0000000 0xe0000fff                                                               |

|                                    | ps7 uart 1 0xe0001000 0xe0001ff                                                                |

|                                    | ps7 l2c 0 0xe0004000 0xe0004fff                                                                |

|                                    | ps7 afi 0 0xf8008000 0xf8008fff                                                                |

|                                    | ps7 afi 1 0xf8009000 0xf8009fff                                                                |

|                                    | ps7_afi_2_0xf800a000_0xf800afff                                                                |

|                                    | ps7_aff_3 0xf800b000 0xf800bfff                                                                |

|                                    | ps7_sd_0 0xe0100000 0xe0100fff                                                                 |

|                                    | ps7_ethernet_0_0xe000b000_0xe000bfff                                                           |

|                                    | ps7_usb_0_0xe0002000_0xe0002fff                                                                |

|                                    | ps7_qspi_0_0xe000d000_0xe000dfff<br>ps7_qspi linear 0_0xfc000000_0xfcffffff                    |

|                                    | ps/_dsp/_intear_0_extensions_extension                                                         |

|                                    | ps7 qpio 0 0xe000a000 0xe00afff                                                                |

|                                    | ps7 ddr 0 0xf8006000 0xf8006fff                                                                |

|                                    | ps7 dev cfg 0 0xf8007000 0xf80070ff                                                            |

|                                    | ps7_xadc_0_0xf8007100_0xf8007120                                                               |

|                                    | pc7 complate comp 0 nuf9000000 nuf900ffff                                                      |

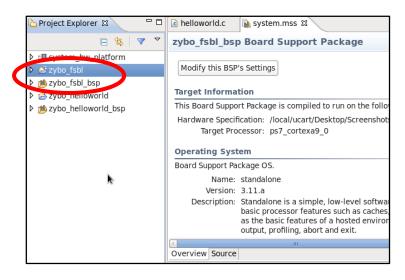

#### 4.2. Creating a new Board Support Package (BSP)

The BSP package is responsible for grabbing all necessary Xilinx library files so they can be called by your program. In other words, it holds the drivers necessary to interface with the hardware on the board.

- 1. Click File and select New->Board Support Package

- 2. In the New Board Support Package Project, enter a project name (system\_bsp in the example).

- 3. Ensure system\_hw\_platform and ps7\_cortexa9\_0 are selected in Target Hardware

- 4. Ensure "standalone" is selected.

- 5. Click Finish to create the BSP

| roject name:  | systen    | n_bsp                                                                                                                                                                                                                                         |            |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 🗸 Use defau   | lt locati | ion                                                                                                                                                                                                                                           |            |

| ocation: //ho | me/pfg    | gerver/Desktop/XPS_walk/sw/system_bsp                                                                                                                                                                                                         | Browse     |

| Cho           | ose file  | system: default   🗘                                                                                                                                                                                                                           |            |

| Target Hardw  | are       |                                                                                                                                                                                                                                               |            |

| Hardware Pla  | tform:    | system_hw_platform                                                                                                                                                                                                                            | 0          |

|               | CPU:      | ps7_cortexa9_0                                                                                                                                                                                                                                | 0          |

| Board Suppor  | t Packa   | age OS                                                                                                                                                                                                                                        |            |

| standalone    |           | Standalone is a simple, low-level software layer. It provides access<br>processor features such as caches, interrupts and exceptions as we<br>basic features of a hosted environment, such as standard input an<br>profiling, abort and exit. | ell as the |

|               |           |                                                                                                                                                                                                                                               |            |

**IMPORTANT:** If UARTO is enabled, follow the steps below, otherwise ensure these are set properly anyway.

6. Click on "standalone" and change the value of stdin AND stdout to ps7\_uart\_1

|                                |                              | Board Support Pa   | ickage settings |                    |                                 |

|--------------------------------|------------------------------|--------------------|-----------------|--------------------|---------------------------------|

| oard Support Package Se        | ttings                       |                    |                 |                    | n.                              |

| ontrol various settings of you | ur Board Support Package.    |                    |                 |                    |                                 |

| Overview                       |                              |                    |                 |                    |                                 |

| orenten                        |                              |                    |                 |                    |                                 |

| standalone                     | Configuration for OS: standa | lone               |                 |                    |                                 |

|                                | Configuration for OS: standa | lone               | Default         | Туре               | Description                     |

| standalone                     | -                            | lone<br>ps7_uart_0 | Default         | Type<br>peripheral | Description<br>stdin peripheral |

| standalone                     | Name                         |                    |                 |                    |                                 |

| standalone                     | Name<br>stdin                | ps7_uart_0         | none            | peripheral         | stdin peripheral                |

7. Click OK when done, you should now see the BSP in the project explorer

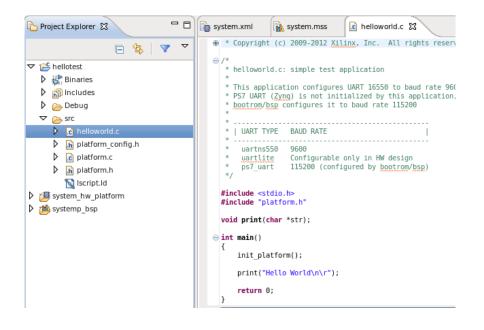

#### 4.3. Creating a new Application Project

Lastly, we have the software program that will run on the board. This is the last piece to the Zybo puzzle, and we're almost there. Projects can be written in C or C++, and can use some standard libraries like stdio, stdlib, string, and otherse. HOWEVER, some libraries (often from Linux) are not implemented like time.h and other things that an OS would handle are not available and other methods must be used. Hopefully you do not run into these instances. (Off topic hint: If you need timing things, check out xtime\_l.h)

1. Click File -> New -> Application Project to open the New Project box

2. Enter a project name, and select the "Use existing" radio button for the BSP. We want to use our newly created one rather than create one.

| •                                            | New Project X                            |

|----------------------------------------------|------------------------------------------|

| Application Project<br>Create a managed make | application project.                     |

| Project nr 📭 hellotest                       |                                          |

| <ul> <li>Use default location</li> </ul>     |                                          |

| Location: //home/pfger                       | ver/Desktop/XPS_walk/sw/hellotest Browse |

| Choose file sy                               | stem: default   \$                       |

| Target Hardware                              |                                          |

| Hardware Platform sy                         | /stem_hw_platform                        |

| Processor p                                  | s7_cortexa9_0                            |

| Target Software                              |                                          |

| OS Platform                                  | standalone                               |

| Language                                     |                                          |

| Board Support Package                        | e O Create New hellotest bsp             |

| <                                            | Use existing systemp_bsp                 |

|                                              |                                          |

| ?                                            | < Back Next > Cancel Finish              |

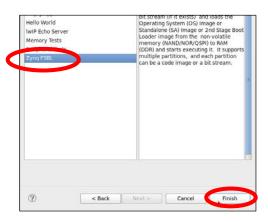

3. Click next and select a template (Hello World is probably best) and hit Finish

| <b>®</b>                                                 | New P           | roject             |              | ×        |

|----------------------------------------------------------|-----------------|--------------------|--------------|----------|

| Templates                                                |                 |                    |              | -        |

| Create one of the available temp<br>application project. | plates to gener | ate a fully-functi | ioning       |          |

| Available Templates:                                     |                 |                    |              |          |

| Dhrystone                                                |                 | Let's say 'Hello   | World' in C. | <u>^</u> |

| Empty Application                                        |                 |                    |              |          |

| Hello World                                              |                 |                    |              |          |

| IwIP Echo Server                                         |                 |                    |              |          |

| Memory Tests                                             |                 |                    |              |          |

| Peripheral Tests                                         |                 |                    |              |          |

| Zynq FSBL                                                |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              | =        |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              | $\sim$   |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

|                                                          |                 |                    |              |          |

| 0                                                        | < Back          | Next >             | Cancel       | Finish   |

4. The new project should appear on the Project Explorer. Expand the project, src, and open the helloworld.c

#### 4.4. Configuring JTAG

We now have all the components, we're now ready to program the board, but wait, we haven't setup how we're going to communicate with the board.

You may now plug in the board to the development computer (yours, Coover machine, etc.)

Flip the switch to power on the board.

- 1. In the menu bar, click Xilinx Tools -> Configure JTAG

- 2. If the board is plugged into Coover 3050-11,-12 or a personal PC, then use Auto Detect (It is ill-advised to be programming the Zybo board from a remote linux machine at this point)

3. Click OK

| hese settings a                                    | affect how XMD connects                                        | to the FPGA. |           | -  |

|----------------------------------------------------|----------------------------------------------------------------|--------------|-----------|----|

| Type:                                              | Auto Detect                                                    |              |           |    |

| Hostname:                                          |                                                                |              |           |    |

| Port:                                              |                                                                |              |           |    |

| Frequency:                                         |                                                                |              |           |    |

| Other Options:                                     |                                                                |              |           |    |

| -                                                  | ain<br>ally Discover Devices on J<br>nfiguration of JTAG Chain |              |           |    |

| Automatica                                         | ally Discover Devices on J                                     |              | 2 i i     |    |

| <ul> <li>Automatica</li> <li>Manual Col</li> </ul> | ally Discover Devices on J                                     |              | • 副 章 등 : | Q. |

| <ul> <li>Automatica</li> <li>Manual Col</li> </ul> | ally Discover Devices on J<br>nfiguration of JTAG Chain        |              |           | Ç. |

| <ul> <li>Automatica</li> <li>Manual Col</li> </ul> | ally Discover Devices on J<br>nfiguration of JTAG Chain        |              |           | Q. |

| <ul> <li>Automatica</li> <li>Manual Col</li> </ul> | ally Discover Devices on J<br>nfiguration of JTAG Chain        |              |           | Q. |

| <ul> <li>Automatica</li> <li>Manual Col</li> </ul> | ally Discover Devices on J<br>nfiguration of JTAG Chain        |              |           | Q. |

#### 4.5. Launching an Application Project

With all our pieces ready to go, we can finally program the board and launch our software program.

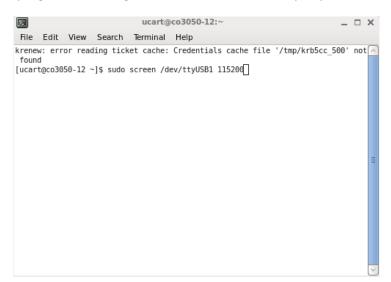

**IMPORTANT:** A COM terminal should be open after the board has been turned on AND before launching the program. Either go through Putty on Windows (COMn Baud 115200) or if through a linux machine (sudo screen /dev/ttyUSB1 115200).

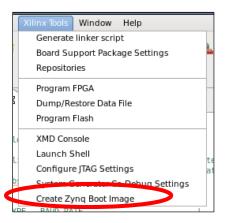

1. On the menu bar, click Xilinx Tools -> Program FPGA, and click Program to start the process

| <u>sop</u>                | Program FPGA X                                                                 |

|---------------------------|--------------------------------------------------------------------------------|

| Program FI<br>Specify the | bitstream and the ELF files that reside in BRAM memory                         |

| -Hardware C               | onfiguration                                                                   |

| Hardware S                | pecification: /home/pfgerver/Desktop/XPS_walk/sw/system_hw_platform/system.xml |

| Bitstream:                | system.bit Search Browse                                                       |

| BMM File:                 | Search Browse                                                                  |

| Software Co               | onfiguration                                                                   |

| Processor                 | ELF File to Initialize in Block RAM                                            |

|                           |                                                                                |

| ?                         | Cancel Program                                                                 |

- 2. If the JTAG configurations and setup were correct, the bitstream should load onto the board and a blue LED should turn on indicating the board is DONE programming.

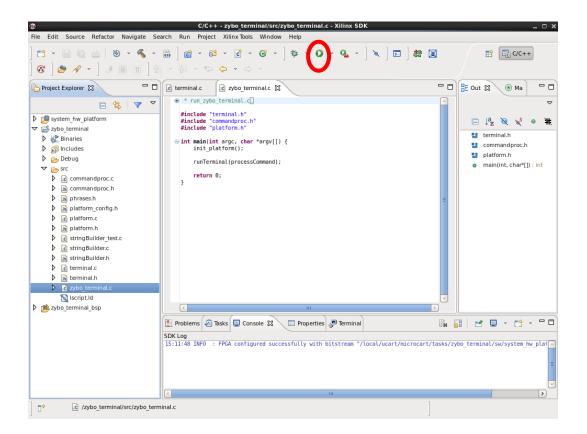

- 3. With the board program, we can now launch our software, click on the Application Project we want to launch and click the Green Play Arrow button to start.

4. View the data received from the board through the COM terminal.

## 5. Running a MicroCART Task Example

We'll run through an example of how to run a MicroCART example. Please, please be read documentation for the task before running it since there might be some peripheral you need to attach first or for other configurations.

#### 5.1. Zybo Board Terminal

1. First, open up XSDK by running xsdk &

- 2. You should now see the workspace prompt come up. Click Browse... and navigate to "tasks/zybo\_terminal/sw".

- 3. Click OK. Do it now, and **DO NOT** check the Use this as the default and do not ask again box.

| ®            | Workspace Launcher                                                                           | ×         |

|--------------|----------------------------------------------------------------------------------------------|-----------|

| Select a wor | kspace                                                                                       |           |

|              | ores your projects in a folder called a workspace.<br>(space folder to use for this session. |           |

| Workspace:   | local/ucart/microcart/tasks/zybo_terminal/sw                                                 | Browse    |

| Use this a   | s the default and do not ask again                                                           |           |

|              |                                                                                              | Cancel OK |

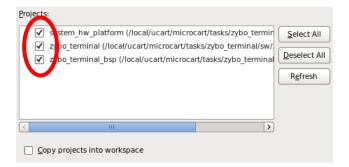

4. Don't be alarmed if the workspace is empty. We just need to import the project that is already there. Click File -> Import ...

5. In the Import window, go to Existing Projects into Workspace under the General folder. Click Next.

| n Import                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ×    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

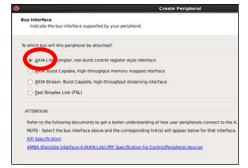

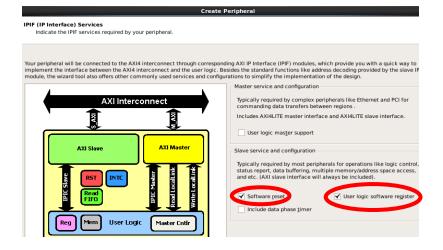

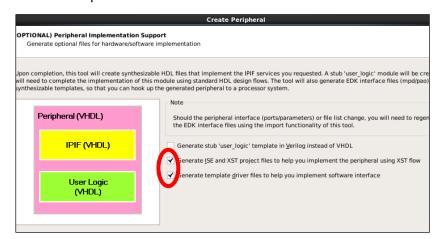

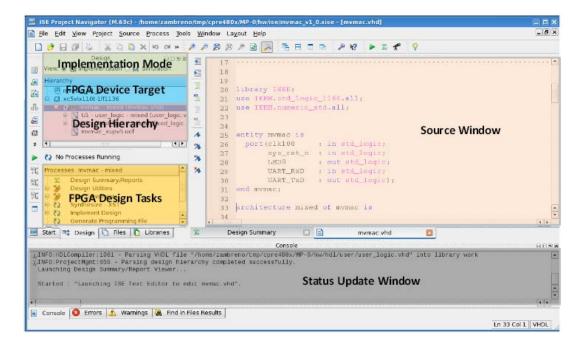

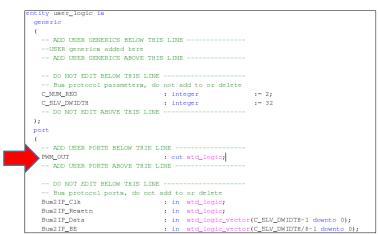

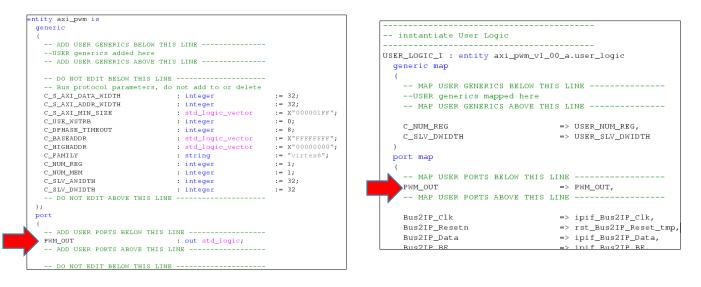

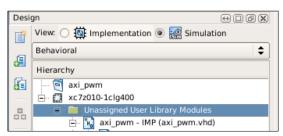

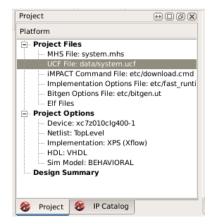

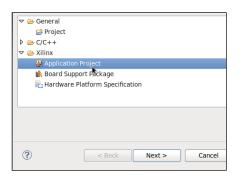

| Select<br>Create new projects from an archive file or directory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ¥1   |